#### the insecurities?

Dave Täht Annoyer-in-Chief Bufferbloat.net

#### IoT Single System Image

- Unlike modern Oses, low end IoT devices have:

- Limited flash

- Severely Limited memory (64k!)

- No MMU

- Nothing we would consider an OS, really

- Programs are overlays, rather than tasks

- Billions of devices like these projected...

- What could go wrong??

#### A piece of IoT Code (from RiotOS)

```

void __attribute__((weak)) free(void *ptr)

```

```

{

```

```

/* who cares about pointers? */

```

```

(void) ptr;

```

```

DEBUG("free(): block at %p lost.\n", ptr);

```

#### Be afraid, be very afraid.

#### My OSI 11 Layer Model

- 0: Historical

- 1: Physical

- 2: Data Link

- 3: Network

- 4 Transport

- 5: Session

- 6: Presentation

- 7: Application

- 8: Individual

- 9: Organizational

- 10: Government

### But our big problems Cross Layers

- 0: Historical

- 1: Physical

- 2: Data Link

- 3: Network

- 4 Transport

- 5: Session

- 6: Presentation

- 7: Application

- 8: Individual

- 9: Organizational

- 10: Government

Motivation Money Communication Security Freedom Latency **Bandwidth**

#### 50 years of computer History

- 0: Historical

- 1: Physical

- 2: Data Link

- 3: Network

- 4 Transport

- 5: Session

- 6: Presentation

- 7: Application

- 8: Individual

- 9: Organizational

- 10: Government

A lot of hardware A lot of code A lot of bad ideas A couple good ones

#### We could make better hardware

- But...

- Hardware design languages and utilities are stuck in the 80s in terms of interoperability and reuse.

- Chipmaking is widely viewed as a monopolists activity

- Promising, more secure architectures vanquished by faster, cheaper ones

- Makers, everywhere, making stuff out of chips, but not making chips!

- FPGAs are cheap and getting cheaper

- 28nm chip making processes are widely available

- Even cpus are now in the design scope of small teams -

- see adapteva, neo, millcomputer, etc

- The system is rotten to its cores!

- We **can** make better cpus and circuits! OpenRisc, Risc-v already exist!

- Plenty of open VHDL/Verilog code available from opencores.org and elsewhere but we can make better hardware design languages like Chisel!

- What would you do with 10 billion transistors?

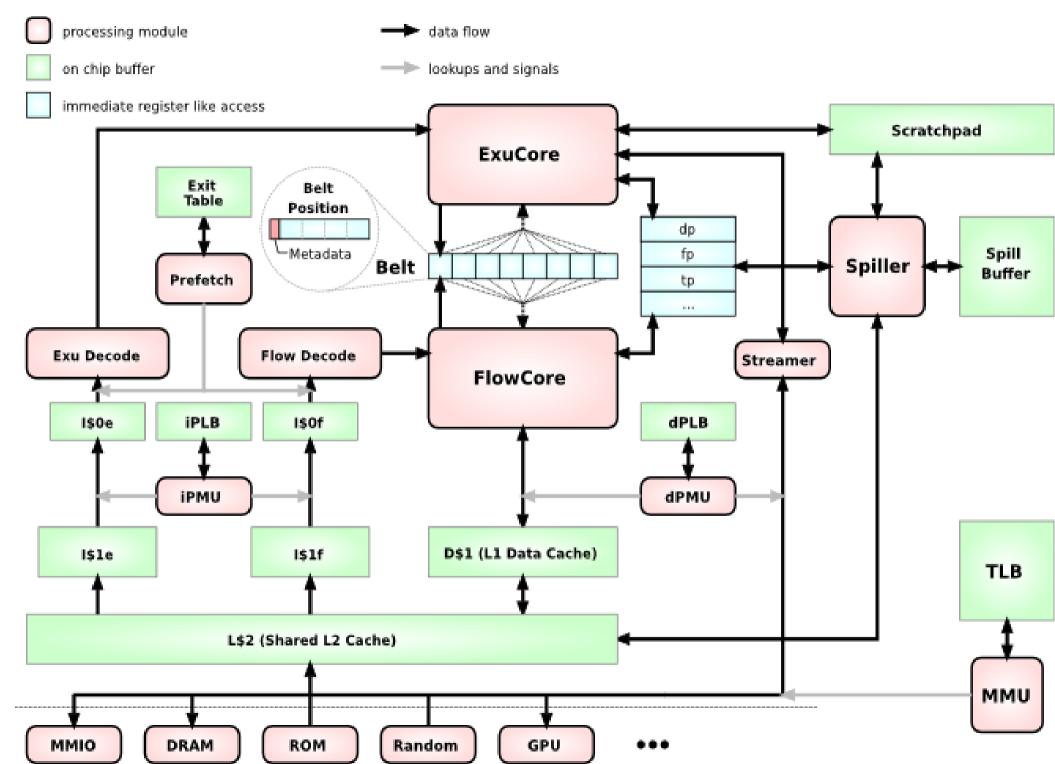

#### Mill Architecture Chart

#### The physical and Data link layers

- 0: Historical

- 1: Physical 🔫

- 2: Data Link 🚽

- 3: Network

- 4 Transport

- 5: Session

- 6: Presentation

- 7: Application

- 8: Individual

- 9: Organizational

- 10: Government

IEEE ITU Materials Scientists Theorists Electrical Engineers

#### The Network and Transport Layers

- 0: Historical

- 1: Physical

- 2: Data Link

- 3: Network 🗨

- 4 Transport 👞

- 5: Session

- 6: Presentation

- 7: Application

- 8: Individual

- 9: Organizational

- 10: Government

IEEE, ACM, Open Source developers, activists

#### Session and Presentation "layers"

- 0: Historical

- 1: Physical

- 2: Data Link

- 3: Network

- 4 Transport

- 5: Session

- 6: Presentation -

- 7: Application

- 8: Individual

- 9: Organizational

- 10: Government

## These don't really exist...

#### Applications

- 0: Historical

- 1: Physical

- 2: Data Link

- 3: Network

- 4 Transport

- 5: Session

- 6: Presentation

- 7: Application  $\blacktriangleright$

- 8: Individual

- 9: Organizational

- 10: Government

# Driving innovations up and down the stack.

#### Individual, Organizational, Governance "Layere"

- 0: Historical

- 1: Physical

- 2: Data Link

- 3: Network

- 4 Transport

- 5: Session

- 6: Presentation

- 7: Application

- 8: Individual 🔺

- 9: Organizational 🔺

- 10: Government

#### aligned? Not.

#### **Action Items**

- Hug an electrical engineer

- Take a politician out to dinner

- Attend a meeting out of your comfort zone

- And write the best code you can.

# Arkyd 3 Cubesat Launch from the ISS (running linux)

#### Do good work!